- 您现在的位置:买卖IC网 > Sheet目录369 > W948D2FBJX5E (Winbond Electronics)IC LPDDR SDRAM 256MBIT 90VFBGA

�� �

�

�

�W948D6FB� /� W948D2FB�

�256Mb� Mobile� LPDDR�

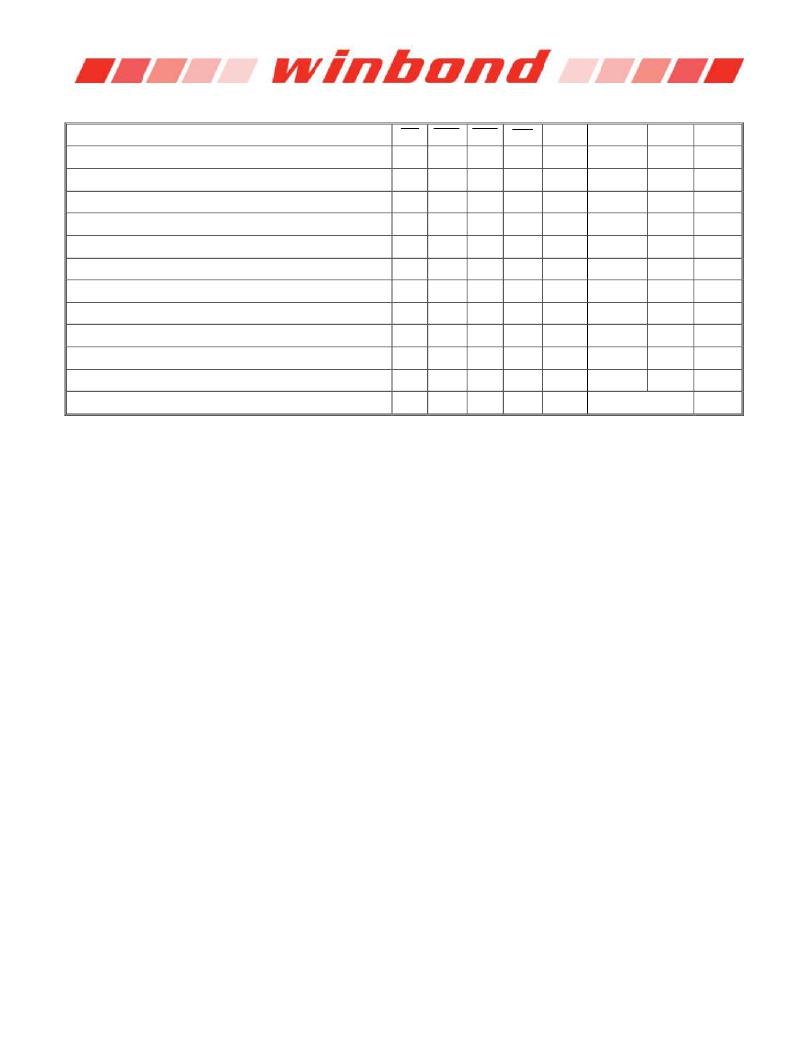

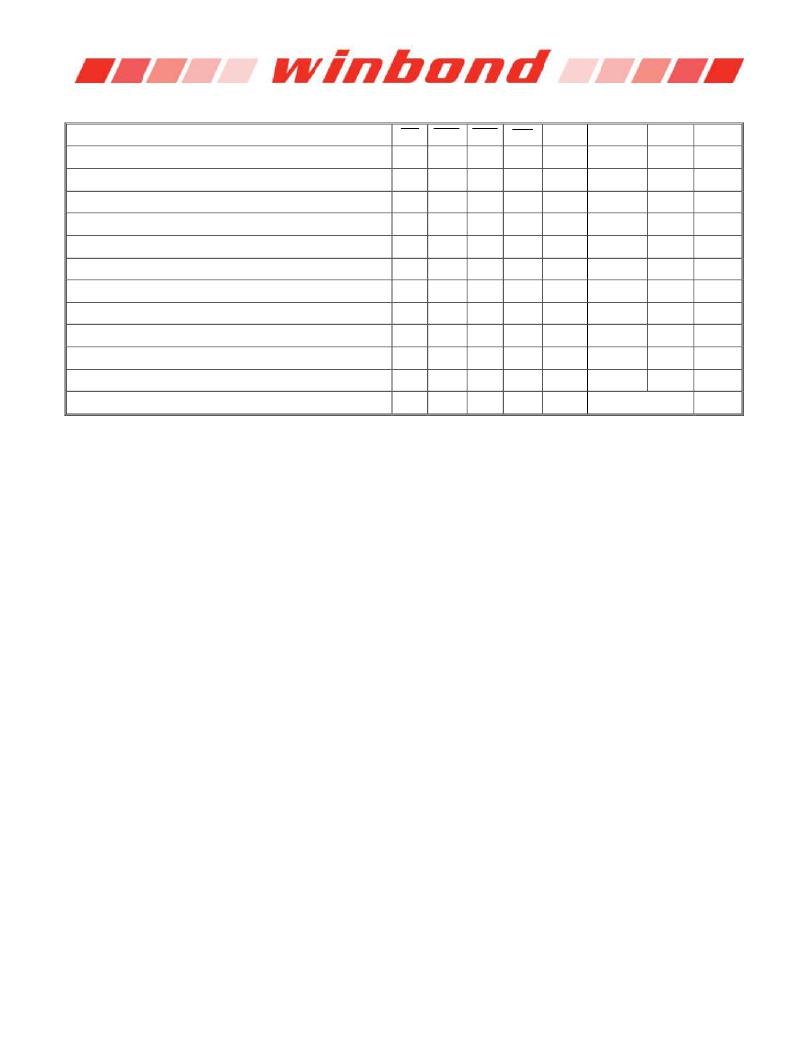

�6.11.2� Truth� Table� -� Commands�

�NAME� (FUNCTION)�

�CS�

�RAS� CAS� WE�

�BA�

�A10/AP� ADDR NOTES�

�DESELECT� (NOP)�

�NO� OPERATION� (NOP)�

�ACTIVE� (Select� Bank� and� activate� row)�

�READ� (Select� bank� and� column� and� start� read� burst)�

�READ� with� AP� (Read� Burst� with� Auto� Precharge)�

�WRITE� (Select� bank� and� column� and� start� write� burst)�

�WRITE� with� AP� (Write� Burst� with� Auto� Precharge)�

�BURST� TERMINATE� or� enter� DEEP� POWER� DOWN�

�PRECHARGE� (Deactivate� Row� in� selected� bank)�

�PRECHARGE� ALL� (Deactivate� rows� in� all� banks)�

�AUTO� REFRESH� or� enter� SELF� REFRESH�

�H�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�L�

�X�

�H�

�L�

�H�

�H�

�H�

�H�

�H�

�L�

�L�

�L�

�X�

�H�

�H�

�L�

�L�

�L�

�L�

�H�

�H�

�H�

�L�

�X�

�H�

�H�

�H�

�H�

�L�

�L�

�L�

�L�

�L�

�H�

�X�

�X�

�Valid�

�Valid�

�Valid�

�Valid�

�Valid�

�X�

�Valid�

�X�

�X�

�X�

�X�

�Row�

�L�

�H�

�L�

�H�

�X�

�L�

�H�

�X�

�X�

�X�

�Row�

�Col�

�Col�

�Col�

�Col�

�X�

�X�

�X�

�X�

�2�

�2�

�3�

�3�

�4,� 5�

�6�

�6�

�7,� 8,� 9�

�MODE� REGISTER� SET�

�L�

�L�

�L�

�L�

�Valid�

�Op-code�

�10�

�Notes:�

�1.�

�2.�

�3.�

�4.�

�5.�

�6.�

�7.�

�8.�

�9.�

�10.�

�11.�

�All� states� and� sequences� not� shown� are� illegal� or� reserved.�

�DESELECT� and� NOP� are� functionally� interchangeable.�

�Auto� precharge� is� non-persistent.� A10� High� enables� Auto� precharge,� while� A10� Low� disables� Auto� precharge.�

�Burst� Terminate� applies� to� only� Read� bursts� with� Autoprecharge� disabled.� This� command� is� undefined� and� should� not� be�

�used� for� Read� with� Auto� precharge� enabled,� and� for� Write� bursts.�

�This� command� is� BURST� TERMINATE� if� CKE� is� High� and� DEEP� POWER� DOWN� entry� if� CKE� is� Low.�

�If� A10� is� low,� bank� address� determines� which� bank� is� to� be� precharged.� If� A10� is� high,� all� banks� are� precharged� and�

�BA0~BA1� are� don?t� care.�

�This� command� is� AUTO� REFRESH� if� CKE� is� High� and� SELF� REFRESH� if� CKE� is� low.�

�All� address� inputs� and� I/O� are� ?don?t� care?� except� for� CKE.� Int� ernal� refresh� counters� control� bank� and� row� addressing.�

�All� banks� must� be� precharged� before� issuing� an� AUTO-REFRESH� or� SELF� REFRESH� command.�

�BA0� and� BA1� value� select� between� MRS� and� EMRS.�

�CKE� is� HIGH� for� all� commands� shown� except� SELF� REFRESH� and� DEEP� POWER-DOWN.�

�Publication� Release� Date� :� Oct,� 15,� 2012�

�-� 20� -�

�Revision� :� A01-004�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W949D2CBJX5E

IC LPDDR SDRAM 512MBIT 90VFBGA

W971GG6JB25I

IC DDR2 SDRAM 1GBIT 84WBGA

W971GG8JB-25

IC DDR2 SDRAM 1GBIT 60WBGA

W9725G6IB-25

IC DDR2-800 SDRAM 256MB 84-WBGA

W9725G6JB25I

IC DDR2 SDRAM 256MBIT 84WBGA

W9725G6KB-25I

IC DDR2 SDRAM 256MBIT 84WBGA

W972GG6JB-3I

IC DDR2 SDRAM 2GBITS 84WBGA

W9751G6IB-25

IC DDR2-800 SDRAM 512MB 84-WBGA

相关代理商/技术参数

W948D2FBJX5ETR

制造商:Winbond Electronics Corp 功能描述:256M MDDR, X32, 200MHZ

W948D2FBJX5I

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR SDRAM 256M-Bit 8Mx32 1.8V 90-Pin VFBGA 制造商:Winbond Electronics Corp 功能描述:IC MEMORY

W948D2FBJX5I TR

制造商:Winbond Electronics Corp 功能描述:256M MDDR, X32, 200MHZ, INDUST

W948D2FBJX6E

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR SDRAM 256M-Bit 8Mx32 1.8V 90-Pin VFBGA 制造商:Winbond Electronics 功能描述:LOW POWER DRAM 制造商:Winbond Electronics Corp 功能描述:IC MEMORY

W948D2FBJX6ETR

制造商:Winbond Electronics Corp 功能描述:256M MDDR, X32, 166MHZ, 65NM

W948D2FBJX6G

制造商:WINBOND 制造商全称:Winbond 功能描述:256Mb Mobile LPDDR

W948D6FB

制造商:WINBOND 制造商全称:Winbond 功能描述:256Mb Mobile LPDDR

W948D6FBHX5E

功能描述:IC LPDDR SDRAM 256MBIT 60VFBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:4G(256M x 16) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP I 包装:Digi-Reel® 其它名称:557-1461-6